DS552 (v1.1) May 5, 2007

## XA2C32A CoolRunner-II Automotive CPLD

**Product Specification**

### **Features**

- AEC-Q100 device qualification and full PPAP support available in both I-grade and extended temperature Q-grade

- Guaranteed to meet full electrical specifications over T<sub>A</sub> = -40° C to +105° C with T<sub>J</sub> Maximum = +125° C (Q-grade)

- Optimized for 1.8V systems

- Industry's best 0.18 micron CMOS CPLD

- Optimized architecture for effective logic synthesis

- Multi-voltage I/O operation: 1.5V through 3.3V

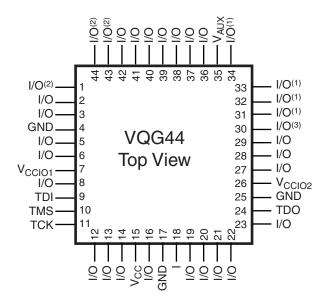

- Available in Pb-free 44-pin VQFP with 33 user I/O

- · Advanced system features

- Fastest in system programming

- 1.8V ISP using IEEE 1532 (JTAG) interface

- IEEE1149.1 JTAG Boundary Scan Test

- Optional Schmitt-trigger input (per pin)

- Two separate I/O banks

- RealDigital 100% CMOS product term generation

- Flexible clocking modes

- · Optional DualEDGE triggered registers

- Global signal options with macrocell control

- Multiple global clocks with phase selection per macrocell

- Multiple global output enables

- · Global set/reset

- Efficient control term clocks, output enables and set/resets for each macrocell and shared across function blocks

- Advanced design security

- Open-drain output option for Wired-OR and LED drive

- Optional configurable grounds on unused I/Os

- Optional bus-hold, 3-state or weak pullup on selected I/O pins

- Mixed I/O voltages compatible with 1.5V, 1.8V,

2.5V, and 3.3V logic levels

- PLA architecture

- Superior pinout retention

- 100% product term routability across function block

- Hot pluggable

Refer to the CoolRunner™-II Automotive CPLD family data sheet for architecture description.

WARNING: Programming temperature range of  $T_A = 0^{\circ}$  C to +70° C

### **Description**

The CoolRunner<sup>™</sup>-II Automotive 32-macrocell device is designed for both high performance and low power applications. This lends power savings to high-end communication equipment and high speed to battery operated devices. Due to the low power stand-by and dynamic operation, overall system reliability is improved

This device consists of two Function Blocks interconnected by a low power Advanced Interconnect Matrix (AIM). The AIM feeds 40 true and complement inputs to each Function Block. The Function Blocks consist of a 40 by 56 P-term PLA and 16 macrocells which contain numerous configuration bits that allow for combinational or registered modes of operation.

Additionally, these registers can be globally reset or preset and configured as a D or T flip-flop or as a D latch. There are also multiple clock signals, both global and local product term types, configured on a per macrocell basis. Output pin configurations include slew rate limit, bus hold, pull-up, open drain and programmable grounds. A Schmitt trigger input is available on a per input pin basis. In addition to storing macrocell output states, the macrocell registers may be configured as "direct input" registers to store signals directly from input pins.

Clocking is available on a global or Function Block basis. Three global clocks are available for all Function Blocks as a synchronous clock source. Macrocell registers can be individually configured to power up to the zero or one state. A global set/reset control line is also available to asynchronously set or reset selected registers during operation. Additional local clock, synchronous clock-enable, asynchronous set/reset and output enable signals can be formed using product terms on a per-macrocell or per-Function Block basis.

The CoolRunner-II Automotive 32-macrocell CPLD is I/O compatible with standard LVTTL and LVCMOS18, LVCMOS25, and LVCMOS33 (see Table 1). This device is also 1.5V I/O compatible with the use of Schmitt-trigger inputs.

Another feature that eases voltage translation is I/O banking. Two I/O banks are available on the CoolRunner-II Automotive 32-macrocell device that permit easy interfacing to 3.3V, 2.5V, 1.8V, and 1.5V devices.

1

© 2006, 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

www.xilinx.com

## RealDigital Design Technology

Xilinx CoolRunner-II Automotive CPLDs are fabricated on a 0.18 micron process technology which is derived from leading edge FPGA product development. CoolRunner-II Automotive CPLDs employ RealDigital, a design technique that makes use of CMOS technology in both the fabrication and design methodology. RealDigital design technology employs a cascade of CMOS gates to implement sum of products instead of traditional sense amplifier methodology. Due to this technology, Xilinx CoolRunner-II Automotive CPLDs achieve both high performance and low power operation.

## Supported I/O Standards

The CoolRunner-II Automotive 32-macrocell device features both LVCMOS and LVTTL I/O implementations. See Table 1 for I/O standard voltages. The LVTTL I/O standard

is a general purpose EIA/JEDEC standard for 3.3V applications that use an LVTTL input buffer and Push-Pull output buffer. The LVCMOS standard is used in 3.3V, 2.5V, 1.8V applications. CoolRunner-II Automotive CPLDs are also 1.5V I/O compatible with the use of Schmitt-trigger inputs.

Table 1: I/O Standards for XA2C32A

| IOSTANDARD Attribute    | Output<br>V <sub>CCIO</sub> | Input V <sub>CCIO</sub> |

|-------------------------|-----------------------------|-------------------------|

| LVTTL                   | 3.3                         | 3.3                     |

| LVCMOS33                | 3.3                         | 3.3                     |

| LVCMOS25                | 2.5                         | 2.5                     |

| LVCMOS18                | 1.8                         | 1.8                     |

| LVCMOS15 <sup>(1)</sup> | 1.5                         | 1.5                     |

(1) LVCMOS15 requires Schmitt-trigger inputs.

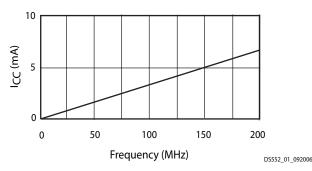

Figure 1: I<sub>CC</sub> vs Frequency

Table 2:  $I_{CC}$  vs Frequency (LVCMOS 1.8V  $T_A = 25^{\circ}C$ )<sup>(1)</sup>

|                              |       | Frequency (MHz) |      |      |      |      |      |      |

|------------------------------|-------|-----------------|------|------|------|------|------|------|

|                              | 0     | 25              | 50   | 75   | 100  | 150  | 175  | 200  |

| Typical I <sub>CC</sub> (mA) | 0.016 | 0.87            | 1.75 | 2.61 | 3.44 | 5.16 | 5.99 | 6.81 |

### Notes:

16-bit up/down, resettable binary counter (one counter per function block).

### **Absolute Maximum Ratings**

| Symbol                           | Description                       | Value       | Units |

|----------------------------------|-----------------------------------|-------------|-------|

| V <sub>CC</sub>                  | Supply voltage relative to ground | -0.5 to 2.0 | V     |

| V <sub>CCIO</sub>                | Supply voltage for output drivers | -0.5 to 4.0 | V     |

| V <sub>JTAG</sub> <sup>(2)</sup> | JTAG input voltage limits         | -0.5 to 4.0 | V     |

| V <sub>CCAUX</sub>               | JTAG input supply voltage         | -0.5 to 4.0 | V     |

| V <sub>IN</sub> <sup>(1)</sup>   | Input voltage relative to ground  | -0.5 to 4.0 | V     |

| V <sub>TS</sub> <sup>(1)</sup>   | Voltage applied to 3-state output | -0.5 to 4.0 | V     |

| T <sub>STG</sub> <sup>(3)</sup>  | Storage Temperature (ambient)     | -65 to +150 | °C    |

| TJ                               | Junction Temperature              | +125        | °C    |

#### Notes:

- Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easiest to achieve. During transitions, the device pins may undershoot to -2.0v or overshoot to +4.5V, provided this over or undershoot lasts less than 10 ns and with the forcing current being limited to 200 mA.

- 2. Valid over commercial temperature range.

- For soldering guidelines and thermal considerations, see the <u>Device Packaging</u> information on the Xilinx website. For Pb free packages, see <u>XAPP427</u>.

## **Recommended Operating Conditions**

| Symbol          | Paran                                              | Min                                                                      | Max | Units |   |

|-----------------|----------------------------------------------------|--------------------------------------------------------------------------|-----|-------|---|

| V <sub>CC</sub> | Supply voltage for internal logic                  | Industrial T <sub>A</sub> = -40°C to +85°C                               | 1.7 | 1.9   | V |

|                 | and input buffers                                  | Q-Grade $T_A = -40^{\circ}\text{C}$ to +105°C,<br>$T_J$ Maximum = +125°C | 1.7 | 1.9   | V |

| $V_{CCIO}$      | Supply voltage for output drivers @                | 3.3V operation                                                           | 3.0 | 3.6   | V |

|                 | Supply voltage for output drivers @ 2.5V operation |                                                                          | 2.3 | 2.7   | V |

|                 | Supply voltage for output drivers @                | 1.8V operation                                                           | 1.7 | 1.9   | V |

|                 | Supply voltage for output drivers @ 1.5V operation |                                                                          | 1.4 | 1.6   | V |

| $V_{CCAUX}$     | JTAG programming pins                              |                                                                          | 1.7 | 3.6   | V |

## DC Electrical Characteristics (Over Recommended Operating Conditions)

| Symbol                         | Parameter                      | Test Conditions                                   | Typical | Max.  | Units |

|--------------------------------|--------------------------------|---------------------------------------------------|---------|-------|-------|

| I <sub>CCSB</sub>              | Standby current Industrial     | V <sub>CC</sub> = 1.9V, V <sub>CCIO</sub> = 3.6V  | 38      | 150   | μА    |

| I <sub>CCSB</sub>              | Standby current Q-grade        | V <sub>CC</sub> = 1.9V, V <sub>CCIO</sub> = 3.6V  | 38      | 550   | μΑ    |

| I <sub>CC</sub> (1)            | Dynamic current                | f = 1 MHz                                         | -       | 1.0   | mA    |

|                                |                                | f = 50 MHz                                        | -       | 4.0   | mA    |

| C <sub>JTAG</sub>              | JTAG input capacitance         | f = 1 MHz                                         | -       | 10    | pF    |

| C <sub>CLK</sub>               | Global clock input capacitance | f = 1 MHz                                         | -       | 12    | pF    |

| C <sub>IO</sub>                | I/O capacitance                | f = 1 MHz                                         | -       | 10    | pF    |

| I <sub>IL</sub> <sup>(2)</sup> | Input leakage current          | V <sub>IN</sub> = 0V or V <sub>CCIO</sub> to 3.9V | -       | +/-10 | μА    |

| I <sub>IH</sub>                | I/O High-Z leakage             | V <sub>IN</sub> = 0V or V <sub>CCIO</sub> to 3.9V | -       | +/-10 | μА    |

#### Notes:

1. 16-bit up/down resettable binary counter (one per Function Block) tested at  $V_{CC} = V_{CCIO} = 1.9V$

# LVCMOS 3.3V and LVTTL 3.3V DC Voltage Specifications

| Symbol            | Parameter                             | Test Conditions                                | Min.                     | Max. | Units |

|-------------------|---------------------------------------|------------------------------------------------|--------------------------|------|-------|

| V <sub>CCIO</sub> | Input source voltage                  |                                                | 3.0                      | 3.6  | V     |

| V <sub>IH</sub>   | High level input voltage              |                                                | 2                        | 3.9  | V     |

| V <sub>IL</sub>   | Low level input voltage               |                                                | -0.3                     | 8.0  | V     |

| V <sub>OH</sub>   | High level output voltage,            | $I_{OH}$ = -8 mA, $V_{CCIO}$ = 3V              | V <sub>CCIO</sub> – 0.4V | -    | V     |

|                   | Industrial grade                      | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 3V$      | V <sub>CCIO</sub> – 0.2V | -    | V     |

|                   | High level output voltage,<br>Q-grade | $I_{OH} = -4 \text{ mA}, V_{CCIO} = 3V$        | V <sub>CCIO</sub> – 0.4V | -    | V     |

|                   |                                       | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 3V$      | V <sub>CCIO</sub> – 0.2V | -    | V     |

| V <sub>OL</sub>   | Low level output voltage,             | I <sub>OL</sub> = 8 mA, V <sub>CCIO</sub> = 3V | -                        | 0.4  | V     |

|                   | Industrial grade                      | $I_{OL}$ = 0.1 mA, $V_{CCIO}$ = 3V             | -                        | 0.2  | V     |

|                   | Low level output voltage,             | I <sub>OL</sub> = 4 mA, V <sub>CCIO</sub> = 3V | -                        | 0.4  | V     |

|                   | Q-grade                               | $I_{OL}$ = 0.1 mA, $V_{CCIO}$ = 3V             | -                        | 0.2  | V     |

# **LVCMOS 2.5V DC Voltage Specifications**

| Symbol            | Parameter                         | Test Conditions                                   | Min.                     | Max.                       | Units |

|-------------------|-----------------------------------|---------------------------------------------------|--------------------------|----------------------------|-------|

| V <sub>CCIO</sub> | Input source voltage              |                                                   | 2.3                      | 2.7                        | V     |

| V <sub>IH</sub>   | High level input voltage          |                                                   | 1.7                      | $V_{\rm CCIO} + 0.3^{(1)}$ | V     |

| V <sub>IL</sub>   | Low level input voltage           |                                                   | -0.3                     | 0.7                        | V     |

| V <sub>OH</sub>   | High level output voltage,        | $I_{OH}$ = -8 mA, $V_{CCIO}$ = 2.3V               | V <sub>CCIO</sub> -0.4V  | -                          | V     |

|                   | Industrial grade                  | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 2.3V$       | V <sub>CCIO</sub> -0.2V  | -                          | V     |

|                   | High level output voltage,        | $I_{OH} = -4 \text{ mA}, V_{CCIO} = 2.3V$         | V <sub>CCIO</sub> -0.4V  | -                          | ٧     |

|                   | Q-grade                           | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 2.3V$       | V <sub>CCIO</sub> – 0.2V | -                          | ٧     |

| $V_{OL}$          | Low level output voltage,         | $I_{OL}$ = 8 mA, $V_{CCIO}$ = 2.3V                | -                        | 0.4                        | ٧     |

|                   | Industrial grade                  | $I_{OL} = 0.1 \text{mA}, V_{CCIO} = 2.3 \text{V}$ | -                        | 0.2                        | V     |

|                   | Low level output voltage, Q-grade | $I_{OL}$ = 4 mA, $V_{CCIO}$ = 2.3V                | -                        | 0.4                        | V     |

|                   |                                   | $I_{OL} = 0.1 \text{mA}, V_{CCIO} = 2.3 \text{V}$ | -                        | 0.2                        | V     |

The V<sub>IH</sub> Max value represents the JEDEC specification for LVCMOS25. The CoolRunner-II input buffer can tolerate up to 3.9V without physical damage.

## **LVCMOS 1.8V DC Voltage Specifications**

| Symbol            | Parameter                            | Test Conditions                                    | Min.                     | Max.                       | Units |

|-------------------|--------------------------------------|----------------------------------------------------|--------------------------|----------------------------|-------|

| V <sub>CCIO</sub> | Input source voltage                 |                                                    | 1.7                      | 1.9                        | V     |

| V <sub>IH</sub>   | High level input voltage             |                                                    | 0.65 x V <sub>CCIO</sub> | $V_{\rm CCIO} + 0.3^{(1)}$ | V     |

| V <sub>IL</sub>   | Low level input voltage              |                                                    | -0.3                     | 0.35 x V <sub>CCIO</sub>   | V     |

| V <sub>OH</sub>   | High level output voltage,           | I <sub>OH</sub> = -8 mA, V <sub>CCIO</sub> = 1.7V  | V <sub>CCIO</sub> – 0.45 | -                          | V     |

|                   | Industrial grade                     | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 1.7V$        | V <sub>CCIO</sub> – 0.2  | -                          | V     |

|                   | High level output voltage, Q-grade   | I <sub>OH</sub> = -4 mA, V <sub>CCIO</sub> = 1.7V  | V <sub>CCIO</sub> – 0.45 | -                          | V     |

|                   |                                      | $I_{OH} = -0.1 \text{ mA}, V_{CCIO} = 1.7V$        | V <sub>CCIO</sub> – 0.2  | -                          | V     |

| V <sub>OL</sub>   | Low level output voltage, Industrial | I <sub>OL</sub> = 8 mA, V <sub>CCIO</sub> = 1.7V   | -                        | 0.45                       | V     |

|                   | grade                                | I <sub>OL</sub> = 0.1 mA, V <sub>CCIO</sub> = 1.7V | -                        | 0.2                        | V     |

|                   | Low level output voltage, Q-grade    | I <sub>OL</sub> = 4 mA, V <sub>CCIO</sub> = 1.7V   | -                        | 0.45                       | V     |

|                   |                                      | I <sub>OL</sub> = 0.1 mA, V <sub>CCIO</sub> = 1.7V | -                        | 0.2                        | V     |

<sup>1.</sup> The V<sub>IH</sub> Max value represents the JEDEC specification for LVCMOS18. The CoolRunner-II input buffer can tolerate up to 3.9V without physical damage.

# LVCMOS 1.5V DC Voltage Specifications<sup>(1)</sup>

| Symbol            | Parameter                            | Test Conditions                                     | Min.                     | Max.                    | Units |

|-------------------|--------------------------------------|-----------------------------------------------------|--------------------------|-------------------------|-------|

| V <sub>CCIO</sub> | Input source voltage                 |                                                     | 1.4                      | 1.6                     | V     |

| $V_{T+}$          | Input hysteresis threshold voltage   |                                                     | 0.5 x V <sub>CCIO</sub>  | 0.8 x V <sub>CCIO</sub> | V     |

| V <sub>T-</sub>   |                                      |                                                     | 0.2 x V <sub>CCIO</sub>  | 0.5 x V <sub>CCIO</sub> | V     |

| V <sub>OH</sub>   | High level output voltage,           | I <sub>OH</sub> = -8 mA, V <sub>CCIO</sub> = 1.4V   | V <sub>CCIO</sub> – 0.45 | -                       | V     |

|                   | Industrial grade                     | I <sub>OH</sub> = -0.1 mA, V <sub>CCIO</sub> = 1.4V | V <sub>CCIO</sub> – 0.2  | -                       | V     |

|                   | High level output voltage, Q-grade   | I <sub>OH</sub> = -4 mA, V <sub>CCIO</sub> = 1.4V   | V <sub>CCIO</sub> – 0.45 | -                       | V     |

|                   |                                      | I <sub>OH</sub> = -0.1 mA, V <sub>CCIO</sub> = 1.4V | V <sub>CCIO</sub> – 0.2  | -                       | V     |

| V <sub>OL</sub>   | Low level output voltage, Industrial | I <sub>OL</sub> = 8 mA, V <sub>CCIO</sub> = 1.4V    | -                        | 0.4                     | V     |

|                   | grade                                | I <sub>OL</sub> = 0.1 mA, V <sub>CCIO</sub> = 1.4V  | -                        | 0.2                     | V     |

|                   | Low level output voltage, Q-grade    | I <sub>OL</sub> = 4 mA, V <sub>CCIO</sub> = 1.4V    | -                        | 0.4                     | V     |

|                   |                                      | I <sub>OL</sub> = 0.1 mA, V <sub>CCIO</sub> = 1.4V  | -                        | 0.2                     | V     |

#### Notes:

## **Schmitt Trigger Input DC Voltage Specifications**

| Symbol            | Parameter                          | Test Conditions | Min.                    | Max.                    | Units |

|-------------------|------------------------------------|-----------------|-------------------------|-------------------------|-------|

| V <sub>CCIO</sub> | Input source voltage               |                 | 1.4                     | 3.9                     | V     |

| V <sub>T+</sub>   | Input hysteresis threshold voltage |                 | 0.5 x V <sub>CCIO</sub> | 0.8 x V <sub>CCIO</sub> | V     |

| V <sub>T-</sub>   |                                    |                 | 0.2 x V <sub>CCIO</sub> | 0.5 x V <sub>CCIO</sub> | V     |

## **AC Electrical Characteristics Over Recommended Operating Conditions**

|                  | -6 -7                                  |      | -6   |      | 7    |       |

|------------------|----------------------------------------|------|------|------|------|-------|

| Symbol           | Parameter                              | Min. | Max. | Min. | Max. | Units |

| T <sub>PD1</sub> | Propagation delay single p-term        | -    | 5.5  |      | 5.5  | ns    |

| T <sub>PD2</sub> | Propagation delay OR array             | -    | 6.0  |      | 6.0  | ns    |

| T <sub>SUD</sub> | Direct input register clock setup time | 2.2  | -    | 2.2  | -    | ns    |

<sup>1.</sup> Hysteresis used on 1.5V inputs.

|                                     |                                                     | -6   |      | -7   |      |       |  |

|-------------------------------------|-----------------------------------------------------|------|------|------|------|-------|--|

| Symbol                              | Parameter                                           | Min. | Max. | Min. | Max. | Units |  |

| T <sub>SU1</sub>                    | Setup time fast (single p-term)                     | 2.6  | -    | 2.6  | -    | ns    |  |

| T <sub>SU2</sub>                    | Setup time (OR array)                               | 3.1  | -    | 3.1  | -    | ns    |  |

| T <sub>HD</sub>                     | Direct input register hold time                     | 0.0  | -    | 0.0  | -    | ns    |  |

| T <sub>H</sub>                      | P-term hold time                                    | 0.0  | -    | 0.0  | -    | ns    |  |

| T <sub>CO</sub>                     | Clock to output                                     | -    | 4.7  | -    | 4.7  | ns    |  |

| F <sub>TOGGLE</sub> <sup>(1)</sup>  | Internal toggle rate                                | -    | 300  | -    | 300  | MHz   |  |

| F <sub>SYSTEM1</sub> <sup>(2)</sup> | Maximum system frequency                            | -    | 200  | -    | 200  | MHz   |  |

| F <sub>SYSTEM2</sub> <sup>(2)</sup> | Maximum system frequency                            | -    | 182  | -    | 182  | MHz   |  |

| F <sub>EXT1</sub> <sup>(3)</sup>    | Maximum external frequency                          | -    | 137  | -    | 137  | MHz   |  |

| F <sub>EXT2</sub> <sup>(3)</sup>    | Maximum external frequency                          | -    | 128  | -    | 128  | MHz   |  |

| T <sub>PSUD</sub>                   | Direct input register p-term clock setup time       | 0.9  | -    | 0.9  | -    | ns    |  |

| T <sub>PSU1</sub>                   | P-term clock setup time (single p-term)             | 1.3  | -    | 1.3  | -    | ns    |  |

| T <sub>PSU2</sub>                   | P-term clock setup time (OR array)                  | 1.8  | -    | 1.8  | -    | ns    |  |

| T <sub>PHD</sub>                    | Direct input register p-term clock hold time        | 1.6  | -    | 1.6  | -    | ns    |  |

| T <sub>PH</sub>                     | P-term clock hold                                   | 1.2  | -    | 1.2  | -    | ns    |  |

| T <sub>PCO</sub>                    | P-term clock to output                              | -    | 6.0  | -    | 6.0  | ns    |  |

| T <sub>OE</sub> /T <sub>OD</sub>    | Global OE to output enable/disable                  | -    | 5.5  | -    | 6.2  | ns    |  |

| T <sub>POE</sub> /T <sub>POD</sub>  | P-term OE to output enable/disable                  | -    | 6.7  | -    | 8.0  | ns    |  |

| T <sub>MOE</sub> /T <sub>MOD</sub>  | Macrocell driven OE to output enable/disable        | -    | 6.9  | -    | 7.6  | ns    |  |

| T <sub>PAO</sub>                    | P-term set/reset to output valid                    | -    | 6.8  | -    | 6.8  | ns    |  |

| T <sub>AO</sub>                     | Global set/reset to output valid                    | -    | 5.5  | -    | 5.5  | ns    |  |

| T <sub>SUEC</sub>                   | Register clock enable setup time                    | 3.0  | -    | 3.0  | -    | ns    |  |

| T <sub>HEC</sub>                    | Register clock enable hold time                     | 0.0  | -    | 0.0  | -    | ns    |  |

| T <sub>CW</sub>                     | Global clock pulse width High or Low                | 2.2  | -    | 2.2  | -    | ns    |  |

| T <sub>PCW</sub>                    | P-term pulse width High or Low                      | 6.0  | -    | 6.0  | -    | ns    |  |

| T <sub>APRPW</sub>                  | Asynchronous preset/reset pulse width (High or Low) | 6.0  | -    | 6.0  | -    | ns    |  |

| T <sub>CONFIG</sub> <sup>(4)</sup>  | Configuration time                                  | -    | 50   | -    | 50   | μs    |  |

#### Notes:

- $F_{\text{TOGGLE}}$  is the maximum clock frequency to which a T-Flip Flop can reliably toggle (see the CoolRunner-II Automotive CPLD family data sheet).

- $F_{SYSTEM1}$  (1/ $T_{CYCLE}$ ) is the internal operating frequency for a device fully populated with one 16-bit counter through one p-term per macrocell while  $F_{SYSTEM2}$  is through the OR array.  $F_{EXT1}$  (1/ $T_{SU1}$ + $T_{CO}$ ) is the maximum external frequency using one p-term while  $F_{EXT2}$  is through the OR array. Typical configuration current during  $T_{CONFIG}$  is 500  $\mu$ A.

# **Internal Timing Parameters**

|                                 |                                        | -6           |           | -7        |     |       |

|---------------------------------|----------------------------------------|--------------|-----------|-----------|-----|-------|

| Symbol Parameter <sup>(1)</sup> |                                        | Min. Max.    |           | Min. Max. |     | Units |

| Buffer Delays                   |                                        |              |           |           | •   |       |

| T <sub>IN</sub>                 | Input buffer delay                     | -            | 1.7       | -         | 1.7 | ns    |

| T <sub>DIN</sub>                | Direct register input delay            | -            | 2.4       | -         | 2.4 | ns    |

| T <sub>GCK</sub>                | Global Clock buffer delay              | -            | 2.0       | -         | 2.0 | ns    |

| T <sub>GSR</sub>                | Global set/reset buffer delay          | -            | 2.0       | -         | 2.0 | ns    |

| T <sub>GTS</sub>                | Global 3-state buffer delay            | -            | 2.1       | -         | 1.5 | ns    |

| T <sub>OUT</sub>                | Output buffer delay                    | -            | 2.0       | -         | 2.0 | ns    |

| T <sub>EN</sub>                 | Output buffer enable/disable delay     | -            | 3.4       | -         | 4.7 | ns    |

| P-term Delays                   |                                        |              | 1         | 1         |     |       |

| T <sub>CT</sub>                 | Control term delay                     | -            | 1.6       | -         | 1.6 | ns    |

| T <sub>LOGI1</sub>              | Single p-term delay adder              | -            | 1.1       | -         | 1.1 | ns    |

| T <sub>LOGI2</sub>              | Multiple p-term delay adder            | -            | 0.5       | -         | 0.5 | ns    |

| Macrocell Dela                  | ay                                     |              | II.       | I.        |     | 1     |

| T <sub>PDI</sub>                | Input to output valid                  | -            | 0.7       | -         | 0.7 | ns    |

| $T_LDI$                         | Setup before clock (transparent latch) | - 2.5 -      |           | 2.5       | ns  |       |

| T <sub>SUI</sub>                | Setup before clock                     | 1.8          | - 1.8     |           | -   | ns    |

| T <sub>HI</sub>                 | Hold after clock                       | 0.0 -        |           | 0.0       | -   | ns    |

| T <sub>ECSU</sub>               | Enable clock setup time                | 1.7 - 1.7    |           | 1.7       | -   | ns    |

| T <sub>ECHO</sub>               | Enable clock hold time                 | 0.0          | -         | 0.0       | -   | ns    |

| T <sub>COI</sub>                | Clock to output valid                  | -            | 0.7       | -         | 0.7 | ns    |

| T <sub>AOI</sub>                | Set/reset to output valid              | -            | 1.5 -     |           | 1.5 | ns    |

| Feedback Dela                   | ays                                    |              |           | 1         |     |       |

| T <sub>F</sub>                  | Feedback delay                         | -            | 1.4       | -         | 1.4 | ns    |

| T <sub>OEM</sub>                | Macrocell to global OE delay           | -            | 0.8 -     |           | 0.2 | ns    |

|                                 | ime Adder Delays 1.5V CMOS             |              | 1         | 1         |     |       |

| T <sub>HYS15</sub>              | Hysteresis input adder                 | - 4.0        |           |           | 4.2 | ns    |

| T <sub>OUT15</sub>              | Output adder                           | -            | 1.0       | 1.0       |     | ns    |

| T <sub>SLEW15</sub>             | Output slew rate adder                 | -            | 5.0       | 5.0       |     | ns    |

|                                 | ime Adder Delays 1.8V CMOS             |              | 1         | 1         | 1   | 1     |

| T <sub>HYS18</sub>              | Hysteresis input adder                 | - 4.0 4.0    |           | 4.0       | ns  |       |

|                                 | Output adder                           | <del> </del> | - 0.0 0.0 |           | 0.0 | ns    |

| T <sub>OUT18</sub>              | Output addel                           |              | 0.0       |           | 0.0 | 110   |

# **Internal Timing Parameters (Continued)**

|                     |                                |      | -6   |      | -7   |       |

|---------------------|--------------------------------|------|------|------|------|-------|

| Symbol              | Parameter <sup>(1)</sup>       | Min. | Max. | Min. | Max. | Units |

| I/O Standard T      | ime Adder Delays 2.5V CMOS     | ·    |      |      |      |       |

| T <sub>IN25</sub>   | Standard input adder           | -    | 0.6  | -    | 0.7  | ns    |

| T <sub>HYS25</sub>  | Hysteresis input adder         | -    | 4.0  | -    | 4.0  | ns    |

| T <sub>OUT25</sub>  | Output adder                   | -    | 0.7  | -    | 0.8  | ns    |

| T <sub>SLEW25</sub> | Output slew rate adder         | -    | 5.0  | -    | 5.5  | ns    |

| I/O Standard T      | ime Adder Delays 3.3V CMOS/TTL |      |      |      |      |       |

| T <sub>IN33</sub>   | Standard input adder           | -    | 0.6  | -    | 0.8  | ns    |

| T <sub>HYS33</sub>  | Hysteresis input adder         | -    | 4.0  | -    | 4.0  | ns    |

| T <sub>OUT33</sub>  | Output adder                   | -    | 1.2  | -    | 1.2  | ns    |

| T <sub>SLEW33</sub> | Output slew rate adder         | -    | 5.0  | -    | 6.6  | ns    |

#### Notes:

## **Switching Characteristics**

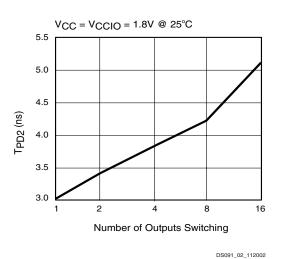

Figure 2: Derating Curve for T<sub>PD</sub>

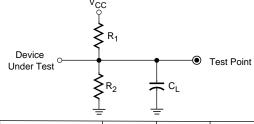

### **AC Test Circuit**

| Output Type | R <sub>1</sub> | R <sub>2</sub> | CL    |

|-------------|----------------|----------------|-------|

| LVTTL33     | 268Ω           | 235Ω           | 35 pF |

| LVCMOS33    | 275Ω           | 275Ω           | 35 pF |

| LVCMOS25    | 188Ω           | 188Ω           | 35pF  |

| LVCMOS18    | 112.5Ω         | 112.5Ω         | 35pF  |

| LVCMOS15    | 150Ω           | 150Ω           | 35pF  |

$<sup>\</sup>mathbf{C}_{\mathbf{L}}$  includes test fixtures and probe capacitance.

DS\_ACT\_08\_14\_02

Figure 3: AC Load Circuit

<sup>1. 1.5</sup> ns input pin signal rise/fall.

<sup>1.5</sup> nsec maximum rise/fall times on inputs.

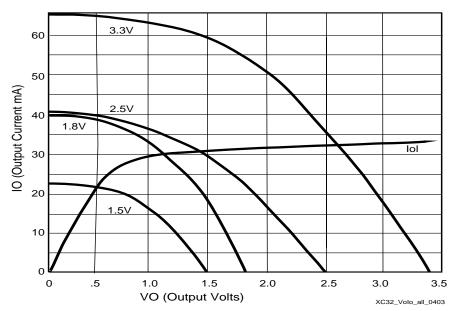

## **Typical I/O Output Curves**

Figure 4: Typical I/V Curve for XA2C32A

# **Pin Descriptions**

| Function Block | Macrocell | VQG44 | I/O Bank |  |  |

|----------------|-----------|-------|----------|--|--|

| 1              | 1         | 38    | Bank 2   |  |  |

| 1              | 2         | 37    | Bank 2   |  |  |

| 1              | 3         | 36    | Bank 2   |  |  |

| 1(GTS1)        | 4         | 34    | Bank 2   |  |  |

| 1(GTS0)        | 5         | 33    | Bank 2   |  |  |

| 1(GTS3)        | 6         | 32    | Bank 2   |  |  |

| 1(GTS2)        | 7         | 31    | Bank 2   |  |  |

| 1(GSR)         | 8         | 30    | Bank 2   |  |  |

| 1              | 9         | 29    | Bank 2   |  |  |

| 1              | 10        | 28    | Bank 2   |  |  |

| 1              | 11        | 27    | Bank 2   |  |  |

| 1              | 12        | 23    | Bank 2   |  |  |

| 1              | 13        | 22    | Bank 2   |  |  |

| 1              | 14        | 21    | Bank 2   |  |  |

| 1              | 15        | 20    | Bank 2   |  |  |

| 1              | 16        | 19    | Bank 2   |  |  |

| 2              | 1         | 39    | Bank 1   |  |  |

| 2              | 2         | 40    | Bank 1   |  |  |

| 2              | 3         | 41    | Bank 1   |  |  |

| 2              | 4         | 42    | Bank 1   |  |  |

| 2(GCK0)        | 5         | 43    | Bank 1   |  |  |

| 2(GCK1)        | 6         | 44    | Bank 1   |  |  |

| 2(GCK2)        | 7         | 1     | Bank 1   |  |  |

# Pin Descriptions (Continued)

| Function Block | Macrocell | VQG44 | I/O Bank |

|----------------|-----------|-------|----------|

| 2              | 8         | 2     | Bank 1   |

| 2              | 9         | 3     | Bank 1   |

| 2              | 10        | 5     | Bank 1   |

| 2              | 11        | 6     | Bank 1   |

| 2              | 12        | 8     | Bank 1   |

| 2              | 13        | 12    | Bank 1   |

| 2              | 14        | 13    | Bank 1   |

| 2              | 15        | 14    | Bank 1   |

| 2              | 16        | 16    | Bank 1   |

#### Notes:

- 1. GTS = global output enable, GSR = global set reset, GCK = global clock

- 2. GTS, GSR, and GCK pins can also be used for general purpose I/O.

### XA2C32A Global, JTAG, Power/Ground and No Connect Pins

| Pin Type                                     | VQG44 <sup>(1)</sup> |

|----------------------------------------------|----------------------|

| TCK                                          | 11                   |

| TDI                                          | 9                    |

| TDO                                          | 24                   |

| TMS                                          | 10                   |

| Input Only                                   | 18 (bank 2)          |

| V <sub>CCAUX</sub> (JTAG supply voltage)     | 35                   |

| Power internal (V <sub>CC</sub> )            | 15                   |

| Power bank 1 I/O (V <sub>CCIO1</sub> )       | 7                    |

| Power bank 2 I/O (V <sub>CCIO2</sub> )       | 26                   |

| Ground                                       | 4,17,25              |

| No connects                                  | -                    |

| Total user I/O (includes dual function pins) | 33                   |

#### Notes:

1. All packages pin compatible with larger macrocell densities

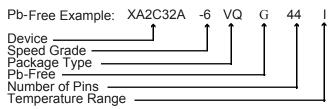

### **Ordering Information**

| Part Number     | Pin/Ball<br>Spacing | θ <sub>JA</sub><br>(C/Watt) | θ <sub>JC</sub><br>(C/Watt) | Package Type        | Package Body<br>Dimensions | I/O | Ind. (I) <sup>(1)</sup><br>Hi-T(Q) |

|-----------------|---------------------|-----------------------------|-----------------------------|---------------------|----------------------------|-----|------------------------------------|

| XA2C32A-6VQG44I | 0.8mm               | 47.7                        | 8.2                         | Very Thin Quad Flat | 10mm x 10mm                | 33  | I                                  |

| XA2C32A-7VQG44Q | 0.0111111           | 71.1                        | 0.2                         | Pack; Pb-free       | TOTALITY TOTALITY          | 55  | Q                                  |

#### Notes:

1. I = Industrial ( $T_A = -40$ °C to +85°C); Q = Automotive ( $T_A = -40$ °C to +105°C with TJ Maximum = +125°C)

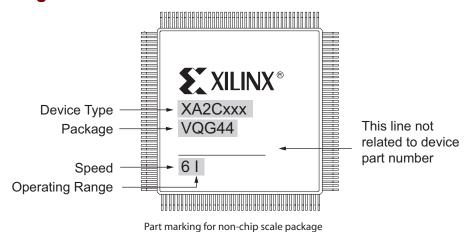

## **Device Part Marking**

Figure 5: Sample Package with Part Marking

- (1) Global Output Enable

- (2) Global Clock

- (3) Global Set/Reset

Figure 6: VQ44 Package

## **CoolRunner-II Automotive Requirements and Recommendations**

### Requirements

The following requirements are for all automotive applications:

- Use a monotonic, fast ramp power supply to power up CoolRunner-II . A V<sub>CC</sub> ramp time of less than 1 ms is required.

- Do not float I/O pins during device operation. Floating I/O pins can increase I<sub>CC</sub> as input buffers will draw 1-2 mA per floating input. In addition, when I/O pins are floated, noise can propagate to the center of the CPLD. I/O pins should be appropriately terminated with bus-hold or pull-up. Unused I/Os can also be configured as C<sub>GND</sub> (programmable GND).

- Do not drive I/O pins without V<sub>CC</sub>/V<sub>CCIO</sub> powered.

- Sink current when driving LEDs. Because all Xilinx CPLDs have N-channel pull-down transistors on outputs, it is required that an LED anode is sourced through a resistor externally to V<sub>CC</sub>. Consequently, this will give the brightest solution.

- Avoid pull-down resistors. Always use external pull-up resistors if external termination is required. This is because the CoolRunner-II Automotive CPLD, which includes some I/O driving circuits beyond the input and

- output buffers, may have contention with external pull-down resistors, and, consequently, the I/O will not switch as expected.

- Do not drive I/Os pins above the V<sub>CCIO</sub> assigned to its I/O bank.

- The current flow can go into V<sub>CCIO</sub> and affect a user voltage regulator.

- It can also increase undesired leakage current associated with the device.

- If done for too long, it can reduce the life of the device.

- Do not rely on the I/O states before the CPLD configures. During power up, the CPLD I/Os may be affected by internal or external signals.

- Use a voltage regulator which can provide sufficient current during device power up. As a rule of thumb, the regulator needs to provide at least three times the peak current while powering up a CPLD in order to guarantee the CPLD can configure successfully.

- Ensure external JTAG terminations for TMS, TCK, TDI, TDO should comply with the IEEE 1149.1. All Xilinx CPLDs have internal weak pull-ups on TDI, TMS, and TCK.

- Attach all CPLD V<sub>CC</sub> and GND pins in order to have necessary power and ground supplies around the CPLD.

- 11. Decouple all  $V_{CC}$  and  $V_{CCIO}$  pins with capacitors of 0.01  $\mu$ F and 0.1  $\mu$ F closest to the pins for each  $V_{CC}/V_{CCIO}$ -GND pair.

- Configure I/Os properly. CoolRunner-II Automotive CPLDs have I/O banks; therefore, signals must be assigned to appropriate banks (LVCMOS33, LVCMOS18...)

#### Recommendations

The following recommendations are for all automotive applications.

- Use strict synchronous design (only one clocking event) if possible. A synchronous system is more robust than an asynchronous one.

- Include JTAG stakes on the PCB. JTAG stakes can be used to test the part on the PCB. They add benefit in reprogramming part on the PCB, inspecting chip internals with INTEST, identifying stuck pins, and inspecting programming patterns (if not secured).

- CoolRunner-II Automotive CPLDs work with any power sequence, but it is preferable to power the V<sub>CCI</sub> (internal V<sub>CC</sub>) before the V<sub>CCIO</sub> for the applications in which any glitches from device I/Os are unwanted.

- 4. Do not disregard report file warnings. Software identifies potential problems when compiling, so the report file is worth inspecting to see exactly how your design is mapped onto the logic.

- Understand the Timing Report. This report file provides a speed summary along with warnings. Read the timing file (\*.tim) carefully. Analyze key signal chains to determine limits to given clock(s) based on logic analysis.

- Review Fitter Report equations. Equations can be shown in ABEL-like format, or can also be displayed in Verilog or VHDL formats. The Fitter Report also includes switch settings that are very informative of other device behaviors.

- 7. Let design software define pinouts if possible. Xilinx CPLD software works best when it selects the I/O pins and manages resources for users. It can spread signals around and improve pin-locking. If users must define pins, plan resources in advance.

- Perform a post-fit simulation for all speeds to identify any possible problems (such as race conditions) that might occur when fast-speed silicon is used instead of slow-speed silicon.

- 9. Distribute SSOs (Simultaneously Switching Outputs) evenly around the CPLD to reduce switching noise.

- 10. Terminate high speed outputs to eliminate noise caused by very fast rising/falling edges.

# **Automotive Warranty Disclaimer**

THIS WARRANTY DOES NOT EXTEND TO ANY IMPLEMENTATION IN AN APPLICATION OR ENVIRONMENT THAT IS NOT CONTAINED WITHIN XILINX SPECIFICATIONS. PRODUCTS ARE NOT DESIGNED TO BE FAIL-SAFE AND ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT OF AIRBAGS. FURTHER, PRODUCTS ARE NOT WARRANTED FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF THE VEHICLE UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE AND ALSO A WARNING SIGNAL TO THE OPERATOR OF THE VEHICLE UPON FAILURE. USE OF PRODUCTS IN SUCH APPLICATIONS IS FULLY AT THE RISK OF CUSTOMER SUBJECT TO APPLICABLE LAWS AND REGULATIONS GOVERNING LIMITATIONS ON PRODUCT LIABILITY.

### **Additional Information**

Additional information is available for the following CoolRunner-II topics:

- XAPP784: Bulletproof CPLD Design Practices

- XAPP375: Timing Model

- XAPP376: Logic Engine

- XAPP378: Advanced Features

- XAPP382: I/O Characteristics

- XAPP389: Powering CoolRunner-II

- XAPP399: Assigning VREF Pins

To access these and all application notes with their associated reference designs, click the following link and scroll down the page until you find the document you want:

CoolRunner-II Data Sheets and Application Notes

<u>Device Packages</u>

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                |  |  |  |

|----------|---------|-------------------------------------------------------------------------|--|--|--|

| 10/31/06 | 1.0     | Initial Xilinx release.                                                 |  |  |  |

| 05/05/07 | 1.1     | Change to V <sub>IH</sub> specification for 3.3V, 2.5V and 1.8V LVCMOS. |  |  |  |